Arm today has announced Safety Ready Program that is aimed to develop solutions for self-driving cars and has also launched the Cortex-A76AE; its first processor IP designed specifically for autonomous vehicles. The Cortex-A76AE processor comes integrated with redundancy and can compute complex relies on up to 16 Cortex-A76 cores.

The Cortex-A76AE can scale to up to 64 cores and has the ability to deliver the aforementioned performance, at high safety integrity. It achieves this through a significant redesign of the Cortex-A76 thus becoming the first high-performance Cortex-A CPU to include the Dual Core Lock-Step (DCLS) and Split-Lock features. The Cortex-A76AE is capable of running in Dual Core Lock-Step (DCLS), and hence is able to contribute towards a system’s ASIL D hardware diagnostic coverage requirements.

It comes with memory protection as standard. It supports Single Error Correction, Double Error Detection (SECDED) ECC and Parity protection in the L1 cache, and SECDED ECC protection with the ability to correct in-line, on the L2 and L3 caches. As a part of the Armv8.2 architecture extension, Cortex-A76AE includes RAS features built in. It also includes comparators, which are integrated into the design.

The Cortex-A76AE has been developed on an advanced process for the avoidance of systematic faults. This enables it to meet the ASIL D systematic requirements as standard. Furthermore, the Quad-issue integer units are integrated into the core including 3x simple ALU and 1x multi-cycle integer. The Cortex-A76AE supports dual-issue native 16B (128-bit) vector and floating-point units, twice the throughput of any previous Arm CPU and 4x ML uplift over Cortex-A75.

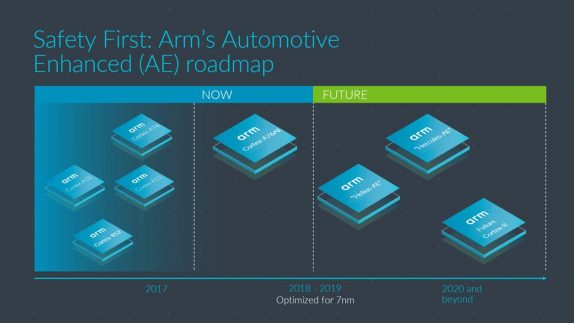

The Arm Safety Ready Program is a multi-year program under which the company will develop Automotive Enhanced (AE) custom and semi-custom solutions for autonomous cars. At launch, the ARM will start with solutions for Level 3 self-driving vehicles, but eventually will offer products built for Level 4 and Level 5 autonomous cars sometimes in 2020 and beyond.

It will include certified physical IP blocks for specific process technologies, ISO 26262-certified software tools, and components, safety documentation. The company is also having plans for Automotive Enhanced processors based on the Helios and the Hercules microarchitectures. It is also planning on offering Automotive Enhanced versions of its future Cortex-R cores sometimes in 2020.